1. 从Flash系统的性能提升说起

从SD卡、手机、平板等消费级产品到数据中心企业级场景,NAND Flash凭借其高性能、大容量、低功耗以及低成本等特性大受欢迎,是目前应用最为广泛的半导体非易失存储介质。为了满足业务场景越来越严苛的性能要求,人们想了许多方法来提升基于NAND Flash的系统性能,具体可分为以下几类:

图一 Flash系统性能提升概览

- 提升总线频率,优化AC Timing:在满足可靠传输的基础上,提升NAND Flash总线频率,尽可能使用较小的时序参数进行操作。特别是在Page Size越来越大(2K 4K 8K 16KB)的情况下,优化时序参数从而减小数据在总线上的传输时间显得尤为重要,这也是过去二十多年来人们一直在持续努力的方向,比如总线接口速率为200Mbps (100MHz)时,完成4KB数据传输需要大约40us,但如果将总线接口速率提升到1600Mbps (800MHz)时,完成4KB数据传输仅需要大约5us。

- 使用Cache Read/Program: 一般情况下,LUN(Logic Unit Number)是NAND Flash最小的逻辑操作单元,读/写操作是串行执行的,即一个读/写命令完成后,才能进行下一个读/写操作。Cache Read/Program允许用户在NAND Flash Array Busy时,同时在总线上进行读/写数据传输,从而提高流水效率。

- 多路并发技术包括:1)通道间并发,允许用户在不同的通道上并发执行独立的命令和数据操作;2)通道内并发,即Interleaving操作,允许用户在满足一定约束的情况下,在通道内的不同CE或CE内的不同Die之间进行交织操作;3)多平面操作,即Multi-Plane操作,允许用户并发读/写Die内的不同Plane。可以说,正是因为有了多路并发技术,才使得基于NAND Flash的固态存储产品能达到GB级别的读/写性能。

可见,以上优化覆盖了NAND Flash基础时序/指令优化到系统级的综合优化,在实际应用中可以根据系统要求组合选用。经过多年发展,Cache Read/Program及多路并发技术已发展得较为成熟,近年来的变化相对较小,但NAND Flash总线频率提升技术一直在蓬勃发展,并且近年来有加速演进的趋势,下面我们将结合ONFI协议演进来感受一下NAND Flash接口速率的演进。

2. ONFI接口演进历史

ONFI (Open NAND Flash Interface)组织成立于2006年5月,致力于简化NAND Flash在消费电子应用和计算平台中的集成和普及。自2006年12月发布第一个ONFI协议以来,ONFI组织已经累计发布了数十个版本,最大接口速率也从最初的50Mbps发展到目前最新的3600Mbps,从图二可以看到ONFI协议不断优化的接口演进趋势。

图二 ONFI接口速率演进

- ONFI 1.0:随着NAND Flash在SD卡及IPod等消费级电子产品的成功应用,以及基于闪存的MP3、U盘等需求量不断增大,极大地拓展了NAND Flash的应用领域。但由于不同NAND Flash厂家的接口协议各有不同,导致下游的主控厂商和产品制造厂商遇到各种兼容性问题。为了改变这种局面,Intel牵头成立了ONFI组织,并在不久后迅速推出ONFI 1.0版本,目的是统一NAND Flash接口协议。

- ONFI 2.x:ONFI 2.x引入了NV-DDR技术,通过双边沿采样(Double Data Rate)实现速率倍增,最大接口速率从ONFI 2.0的133Mbps演进到ONFI 2.1/2.2的200Mbps。NV-DDR技术引入外部参考电压作为数据输入/输出信号的采样基准,采用源同步时钟来精确锁存数据、命令、地址信号,但由于DQS和Clock不是差分信号,所以边沿容易受干扰,目前主流消费级/企业级NAND Flash已经很少看到NV-DDR接口。

- ONFI 3.x:ONFI 3.x引入了NV-DDR2技术,最大接口速率从ONFI 3.0/3.1的400Mbps演进到ONFI 3.2的533Mbps。NV-DDR2引入了差分信号和On-Die Termination (ODT)技术来提升信号质量。在差分模式下,通过在数据传输阶段使能RE_n/RE_c差分信号对和DQS_t/DQS_c signals差分信号对,可有效抑制噪声和干扰。通过在NAND Flash芯片上集成ODT端接电阻,可以将控制器和NAND Flash的信号传输通道上的阻抗失配减少到最小,有助于减少信号反射;另外,ODT阻值可以通过软件配置寄存器来控制,因此可以大大简化硬件电路设计。

- ONFI 4.x:ONFI 4.x引入了NV-DDR3技术,最大接口速率从ONFI 4.0的800Mbps演进到ONFI 4.2的1600Mbps。为保障高速信号传输质量,NV-DDR3引入了多项校准技术,包括ZQ Calibration、Duty Cycle Correction (DCC)和读/写DQ校准。上文提到ONFI 3.0引入了ODT技术,由于NAND Flash上的ODT电阻采用CMOS工艺制备,容易在温度和电压变化时发生阻值漂移,因此需要通过ZQ Calibration技术通过外接高精度电阻进行阻值校准。DCC校准可调节信号占空比,解决高速信号传输路径不对称导致的上升沿与下降沿失配问题,而读/写DQ校准可以保证读/写采样信号对准眼图中心。

- ONFI 5.x:ONFI 5.x引入了NV-LPDDR4技术,最大接口速率从ONFI 5.0的2400Mbps演进到ONFI 5.1的3600Mbps。为了解决高速接口带来的巨大信号完整性挑战,ONFI 5.x除了进一步加强写校准和VrefQ校准外,还引入了非对称DQS设计和自适应均衡器设计。如DFE(ecision Feedback Equalizer,判决反馈均衡器)技术用上次信道的输出经过判断后加权反馈到输入上,可以消除码后干扰。另外,NV-DDR3和NV-LPDDR4支持的最大接口速率相同,但NV-LPDDR4的优势在于采用LTT技术后可大幅度降低读操作功耗。

从ONFI 1.0到近期最新发布的ONFI 5.1可以看出,为了匹配系统前端接口(如eMMC/UFS/PCIe)越来越高的带宽要求,NAND Flash接口速率整整提升了72倍,而且未来还将快速走向下一个峰值。

那接口速率的提升给系统带来的收益是否也在翻倍上涨呢?答案是否定的。

3. 传统协议的不足呼唤进一步改进

NAND Flash总线上传输的信号可分为命令、地址和数据3种,通过DQ[7:0]时分复用,在不同的时刻分别传输命令、地址和数据。其中,数据是同步传输、差分采样,速率较高;但命令和地址是异步传输、单端采样,速率较低。从ONFI 1.0到ONFI 5.1,接口速率得到了飞速发展,但命令、地址和数据的传输形式基本不变。实际上,随着总线速率提升,改善的主要是数据传输时延,命令和地址的传输时延并没有得到改善,对系统而言总线使用效率是在不断下降的。如下图三在乐观的场景下比较了写/读场景的总线效率,可以看到,读和写的总线效率都在逐渐降低,尤其是在读场景跌落到50%左右时进一步加剧了系统设计的挑战。

图三 NAND Flash总线效率分析

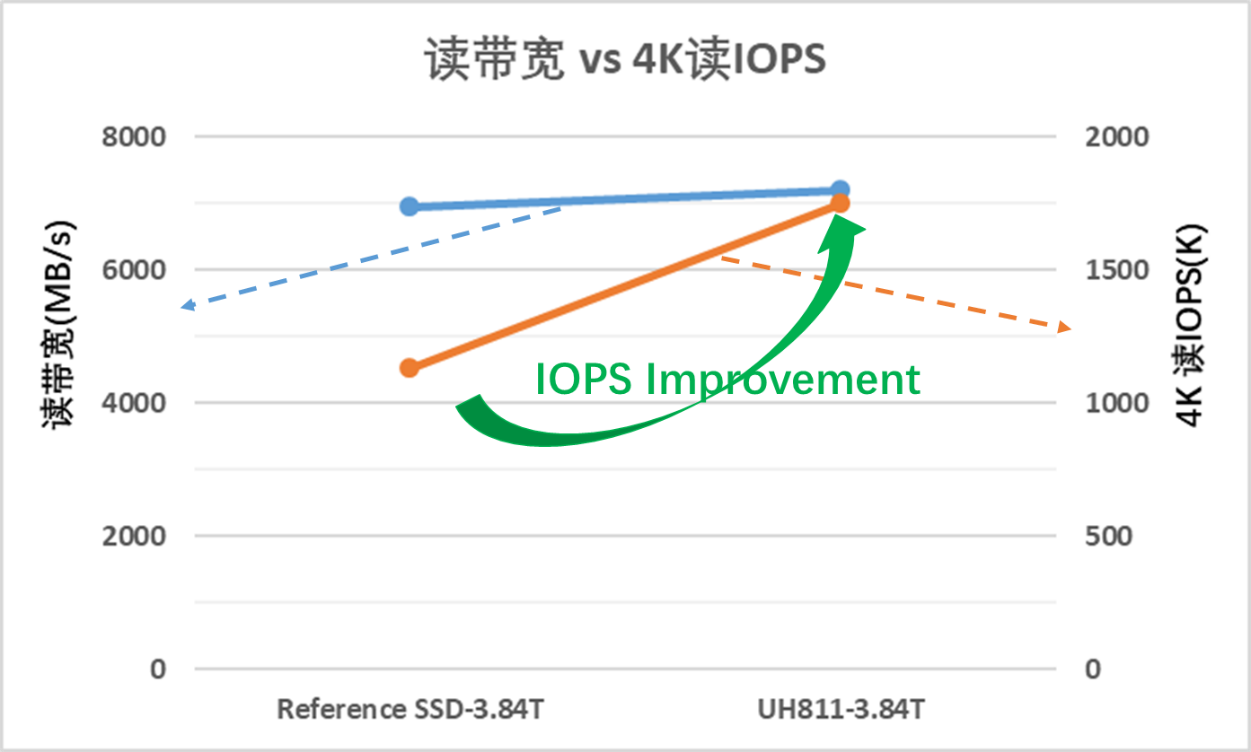

图四以业内某型号SSD为参考,与忆联企业级固态硬盘产品UH811a进行了对比分析。可以看到,两款SSD的读带宽相当,都在7000MB/s左右,但UH811a的4K随机读IOPS相比参考SSD有显著提升。进一步分析可以发现,将UH811a的4K IOPS换算成带宽,是与读带宽相当的;但对参考SSD进行同样的换算,则换算出来的带宽只有读带宽的70%,原因就在于随机读操作的总线开销高于顺序读。

图四 读带宽 vs 4K读IOPS

可见,在传统命令/地址/数据传输形式不变的情况下,随着接口速率提升,增加系统复杂度的同时,带来的收益却在衰减,因此,传统协议的不足推动协议不断改进。面对这个问题,JEDEC组织正紧锣密鼓地讨论协议的下一轮演进,未来将在提升接口速率的同时优化命令/地址传输方式,这也势必会给主控设计带来新的考验。

4. 总结

一直以来,提升NAND Flash接口速率是提高系统性能的主要手段,NAND Flash厂商也想出了各种办法来解决高速信号带来的信号完整性问题。面向未来,传统的命令/地址输入方式导致总线利用率不高,协议的进一步演进除了考虑继续提升接口速率外,也将迎来新的命令/地址输入方式。忆联将密切关注协议发展动态,并以灵活的架构来兼容支持未来的介质,给客户带来更好的存储产品与解决方案。

参考资料:

1. ONFI spec:

http://www.onfi.org/specifications

2.2022, Phison, NAND Flash 101: Flash Device Interfaces:

https://phisonblog.com/nand-flash-101-flash-device-interfaces-2/

3.2021, 移动NAND闪存存储的演进:

https://phisonblog.com/the-evolution-of-mobile-nand-flash-memory-storage-2/

4.芯片中的数学——均衡器EQ和它在高速外部总线中的应用:

https://zhuanlan.zhihu.com/p/48343011